L'emploi scientifique et technique

direction de la recherche technologique

Qui sommes nous ?

- Nous œuvrons quotidiennement pour un futur désirable.

- Nous avons plus de 50 ans d’existence.

- Nous déposons plus de 600 brevets par an.

- Nous formons un ensemble composé de quatre instituts (List, Leti, Liten, CEA Reg)

- Nous relevons 19 défis prioritaires pour la société grâce à nos 54 plateformes technologiques de rang mondial.

- Nous sommes un collectif pluridisciplinaire de plus 4.000 personnes aux profils scientifiques, techniques ou administratifs.

Êtes-vous prêts à devenir un citoyen avec un métier qui a de l’impact ?

Êtes-vous prêts à rejoindre un organisme et être utile aux entreprises, à la société, à la planète ?

Nous avons le pouvoir d’agir et nous vous proposons de vous en servir !

La DRT du CEA, en quelques chiffres :

Consultez nos dernières opportunités

- Doctorat

- Contrat à durée déterminée

- Contrat à durée déterminée

- Contrat à durée déterminée

- Contrat à durée indéterminée

- Contrat à durée indéterminée

- Contrat à durée déterminée

- Contrat à durée indéterminée

- Contrat à durée déterminée

Pourquoi nous rejoindre

Rejoindre la DRT du CEA, c’est intégrer un collectif soudé de 4 000 chercheurs, ingénieurs et techniciens repartis sur nos implantions historique de Paris-Saclay et Grenoble, ou en région.

C’est être accompagné et soutenu par des experts reconnus dans leurs domaines. C’est avoir les clés pour développer ses compétences.

Rejoindre nos équipes de recherche, c’est évoluer dans les meilleurs écosystèmes d’innovation français et européens. C’est coopérer avec les acteurs les plus innovants du territoire pour tester de nouvelles idées et repousser les limites.

Que votre métier soit scientifique, technique ou administratif, rejoindre la DRT du CEA c’est contribuer à construire un futur plus désirable en :

- Développant des solutions matérielles et logicielles au service d’un numérique frugal et responsable

- Favorisant l’émergence d’énergie bas-carbone et en réduisant la consommation des ressources

- Imaginant la médecine du futur, plus personnalisée, plus humaine et plus efficace

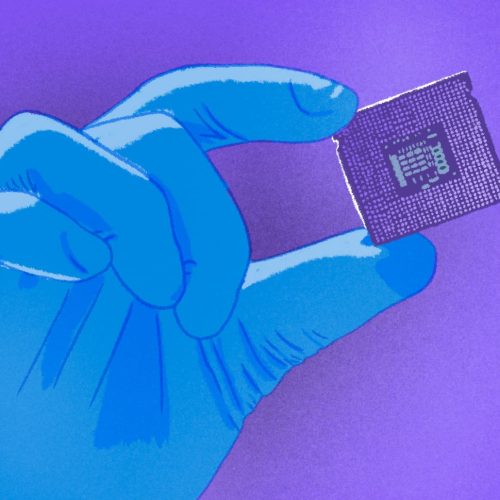

- Garantissant la souveraineté technologique et industrielle ainsi que l’autonomie stratégique de la France.

grâce à une concentration d’expertises, de moyens logiciels et de matériels de pointe unique en Europe.

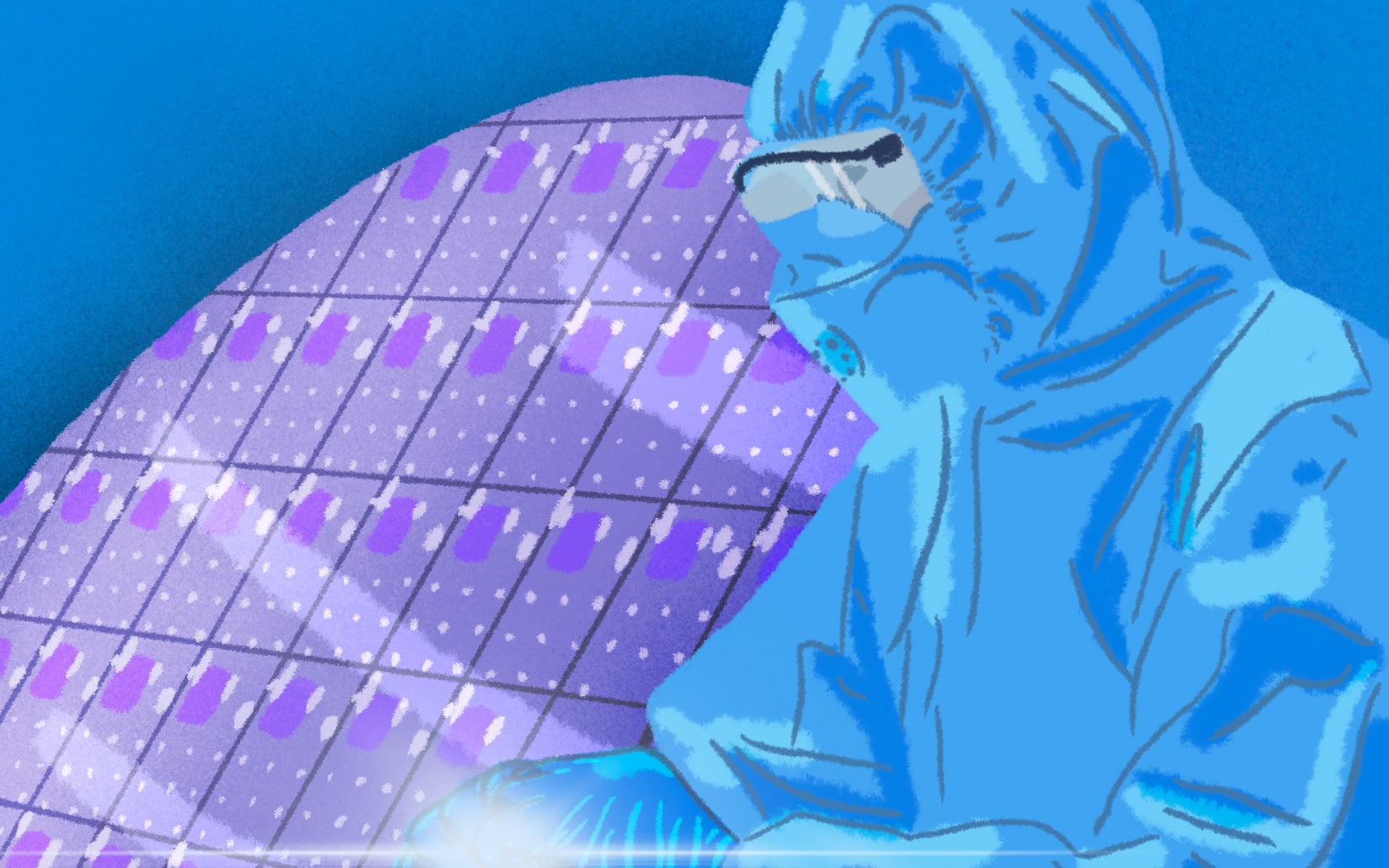

Avec plus de 50 plateformes technologiques au niveau des plus hauts standards industriels et une concentration d’expertises et de moyens unique en Europe, nos équipes développent dans des délais optimisés, des produits innovants, protégés par une propriété intellectuelle forte.

Avec un portefeuille de 6 500 familles de brevets actifs, la DRT s’impose comme un acteur majeur de la recherche technologique, en France, en Europe, mais également à l’échelle mondiale.

Chaque année, sa politique volontariste en matière de propriété intellectuelle la conduit à déposer plus de 600 nouveaux brevets prioritaires.

Devenir doctorant

au cea

Devenir doctorant au CEA, c’est une opportunité exceptionnelle pour les étudiants souhaitant s’engager dans une carrière de chercheur.

Être doctorant au CEA, c’est travailler sur des projets de recherche innovants, en réponse aux défis technologiques de l’industrie et de la société, pour un futur désirable.

Être doctorant au CEA, c’est bénéficier d’une formation scientifique de haut niveau, d’un encadrement personnalisé et d’un accès à des installations de recherche ainsi qu’à des équipements à l’état de l’art mondial.

Encadré par des experts renommés, nos doctorants évoluent dans un environnement de travail collaboratif et stimulant, où ils peuvent développer leurs compétences et être force de proposition pour faire progresser la science.

Être doctorant au CEA, c’est l’opportunité pour développer son réseau à travers des collaborations étroites avec les partenaires industriels et académiques du CEA.

Devenez doctorant.

Rejoignez les équipes de recherche du CEA et marquez votre temps !

Découvrez nos défis technologiques

Actualités

Toutes les news

La campagne de recrutement des alternants de la Direction de la Recherche Technologiques est lancée ! Chaque année, nous recrutons plus de 150 alternants. Du […]

Grenoble, 4 avril 2024 – La Direction de la Recherche Technologique du CEA (DRT) a accueilli les étudiants de l’ENSE3 pour une journée immersive, révélant […]

Le CEA se distingue à nouveau dans le classement TOP 100 Global Innovators 2024 de Clarivate, se classant 31ème et marquant ainsi sa 12ème présence […]